Virtual Memory

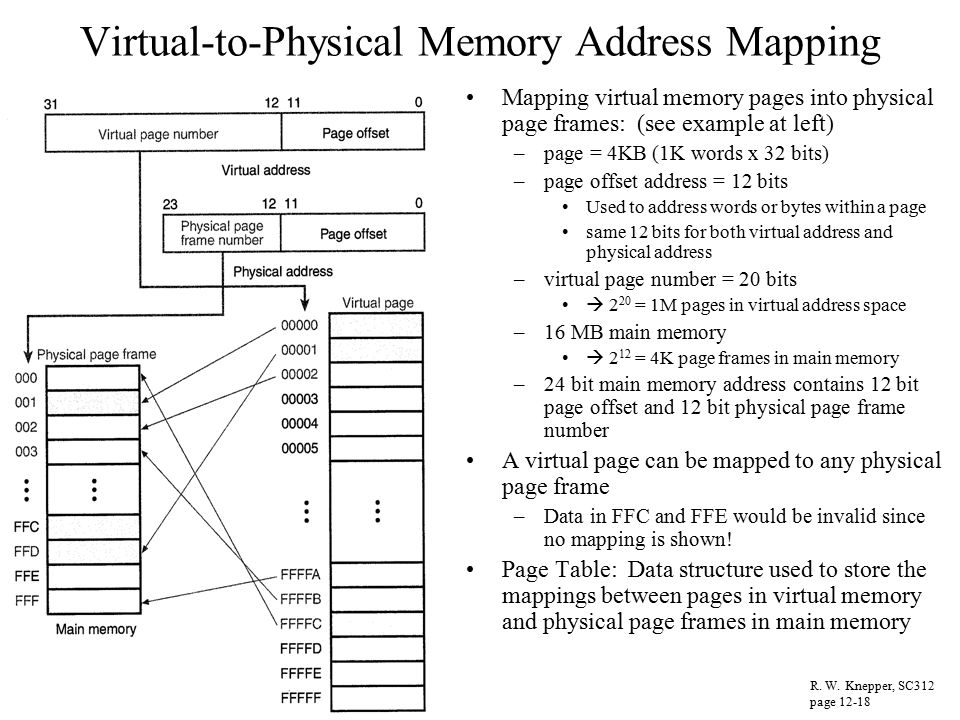

- We will break both address spaces up into “pages”.

- Typically 4KB in size, although sometimes large

- Use a “page table” to map between virtual pages and physical pages.

- The processor generates “virtual” addresses

- They are translated via “address translation” into physical addresses.

from http://cseweb.ucsd.edu/classes/wi11/cse141/Slides/19_VirtualMemory.key.pdf

- build a cache for the page mapping, but call it a “translation lookaside buffer” or “TLB”

- TLBs are small (maybe 128 entries), highly-associative (often fully-associative) caches for page table entries.

- Virtual memory to Physical memory mapping